在单片机与外围设备的通信中,SPI总线是一种常用的通信方式。SPI是英文"Serial Periphral Interface"的缩写,中文翻译为"串行外围设备接口"。今天这篇文章,我们就来谈谈SPI通信的原理,并详细讨论下总线时钟的极性与相位。

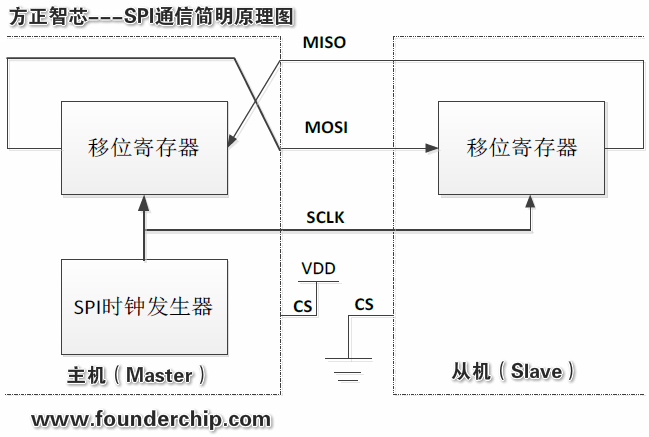

SPI(Serial Periphral Interface)最早是由摩托罗拉公司设计并实现,它是一种高速的、全双工的通信总线,采用主机(Master)-从机(Slave)的方式进行通信。SPI占用芯片的四个引脚,也就是说采用四条信号线来进行通信。这四条线分别是:主设备输入与从设备输出线(Master In Slave Out,MISO);主设备输出与从设备输入线(Master Out Slave In,MOSI);串行同步时钟信号线(Serial Clock,SCK);外围设备片选信号线(Slave Selection,SS)。

SPI总线的主机和从机都有一个移位寄存器,当主机向自己的移位寄存器写入数据时,数据会通过MOSI信号线进入到从机的移位寄存器;同时,从机移位寄存器里的数据,通过MISO信号线进入到主机的移位寄存器。这样,主机和从机就完成了一次数据交换。下面这张图,是SPI通信的简明原理图:

SPI数据的传输是在串行同步时钟信号(Serial Clock,SCK)的控制下进行的。主机的时钟发生器一方面控制主机的移位寄存器,另一方面通过从机的SCK信号线来控制从机的移位寄存器,从而保证主机与从机的数据交换是同步进行的。

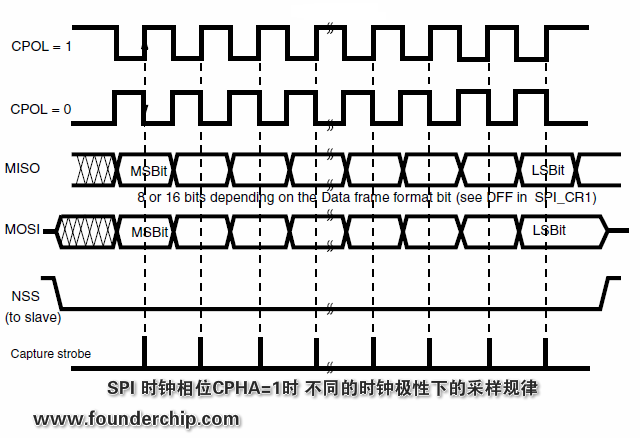

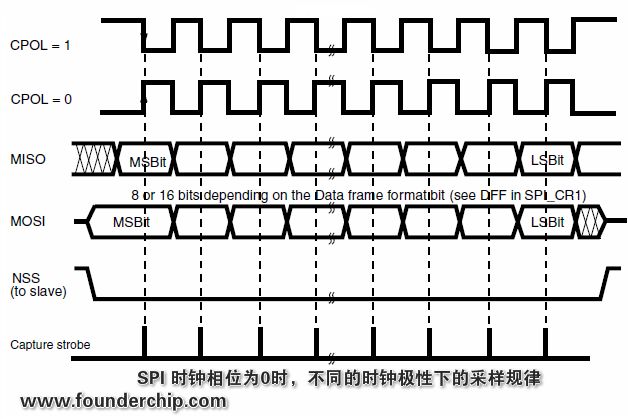

SPI串行同步时钟可以设置为不同的极性(Clock Polarity ,CPOL)与相位(Clock Phase ,CPHA)。

时钟的极性(CPOL)用来决定在总线空闲时,同步时钟(SCK)信号线上的电位是高电平还是低电平。当时钟极性为0时(CPOL=0),SCK信号线在空闲时为低电平;当时钟极性为1时(CPOL=1),SCK信号线在空闲时为高电平;

时钟的相位(CPHA)用来决定何时进行信号采样。

当时钟相位为1时(CPHA=1),在SCK信号线的第二个跳变沿进行采样;这里的跳变沿究竟是上升沿还是下降沿?取决于时钟的极性。当时钟极性为0时,取下降沿;当时钟极性为1时,取上升沿;如下图:

当时钟相位为0时(CPHA=0),在SCK信号线的第一个跳变沿进行采样。跳变沿同样与时钟极性有关:当时钟极性为0时,取上升沿;当时钟极性为1时,取下降沿;如下图:

在STM32系列单片机中,可以通过SPI_CR1寄存器来设置时钟的极性(CPOL)与相位(CPHA)。

好了,关于SPI通信就先介绍到这里,欢迎扫描下的二维码关注我们的微信公众号。

北岛夜话

北岛夜话

发表评论